#### EC64 VLSI DESIGN SYLLABUS

#### **UNIT I CMOS TECHNOLOGY**

A brief History-MOS transistor, Ideal I-V characteristics, C-V characteristics, Non ideal IV effects, DC transfer characteristics - CMOS technologies, Layout design Rules, CMOS process enhancements, Technology related CAD issues, Manufacturing issues

#### UNIT II CIRCUIT CHARACTERIZATION AND SIMULATION

Delay estimation, Logical effort and Transistor sizing, Power dissipation, Interconnect, Design margin, Reliability, Scaling- SPICE tutorial, Device models, Device characterization, Circuit characterization, Interconnect simulation

## UNIT III COMBINATIONAL AND SEQUENTIAL CIRCUIT DESIGN

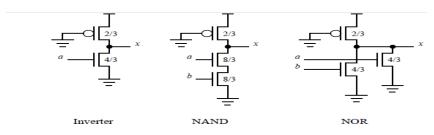

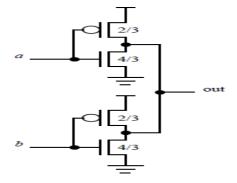

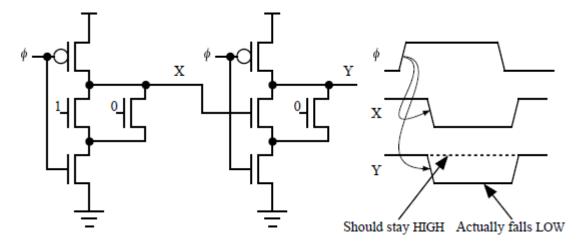

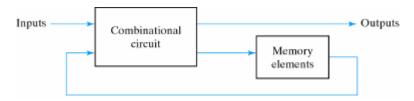

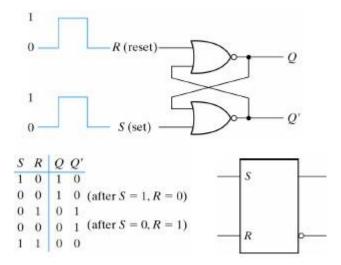

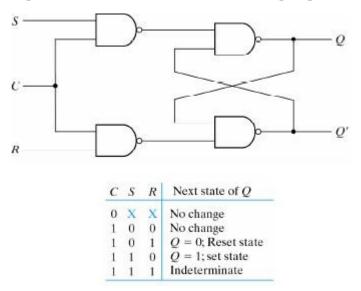

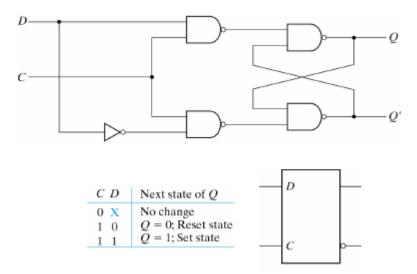

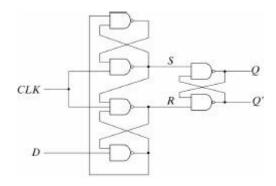

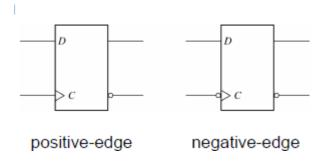

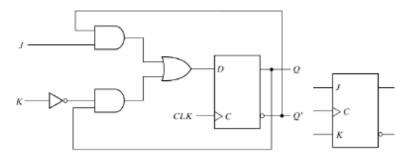

Circuit families –Low power logic design – comparison of circuit families – Sequencing static circuits, circuit design of latches and flip flops, Static sequencing element methodology- sequencing dynamic circuits – synchronizers

#### UNIT IV CMOS TESTING

Need for testing- Testers, Text fixtures and test programs- Logic verification- Silicon debug principles- Manufacturing test – Design for testability – Boundary scan

#### UNIT V SPECIFICATION USING VERILOG HDL

Basic concepts- identifiers- gate primitives, gate delays, operators, timing controls, procedural assignments conditional statements, Data flow and RTL, structural gate level switch level modeling, Design hierarchies, Behavioral and RTL modeling, Test benches, Structural gate level description of decoder, equality detector, comparator, priority encoder, half adder, full adder, Ripple carry adder, D latch and D flip flop.

#### Textbooks:

- 1. Weste and Harris: CMOS VLSI DESIGN (Third edition) Pearson Education, 2005

- 2. Uyemura J.P: Introduction to VLSI circuits and systems, Wiley 2002.

- 3. J.Bhasker,"Verilog HDl Primer", BS publication,2001(UNIT V)

#### **References:**

- 1 D.A Pucknell & K.Eshraghian Basic VLSI Design, Third edition, PHI, 2003

- 2 Wayne Wolf, Modern VLSI design, Pearson Education, 2003

- 3 M.J.S.Smith: Application specific integrated circuits, Pearson Education, 1997

- 4 Ciletti Advanced Digital Design with the Verilog HDL, Prentice Hall of India, 2003

#### UNIT I CMOS TECHNOLOGY

# INTRODUCTION

An MOS (Metal-Oxide-Silicon) structure is created by superimposing several layers of conducting, insulating, and transistor forming materials. After a series of processing steps, a typical structure might consists of levels called diffusion, polysilicon, and metal that are separated by insulating layers. CMOS technology provides two types of transistors, an n-type transistor (n MOS) and a p-type transistor (p MOS). These are fabricated in silicon by using either negatively doped silicon that is rich in electrons (negatively charged) or positively doped silicon that is rich in holes (the dual of electrons and positively charged). For the n-transistor, the structure consists of a section of p-type silicon separating two diffused areas of n-type silicon. The area separating the n regions is capped with a sandwich consisting of an insulator and a conducting electrode called the GATE. Similarly, for the p-transistor the structure consists of a section of n-type silicon separating two p-type diffused areas. The p-transistor also has a gate electrode. The gate is a control input and it affects the flow of electrical current between the drain and source. The drain and source may be viewed as two switched terminals.

An MOS transistor is termed a majority-carrier device, in which the current in a conducting channel between the source and drain is modulated by a voltage applied to the gate. In an n-type MOS transistor (i.e.,nMOS), the majority carriers are electrons. A positive voltage applied on the gate with respect to the substrate enhances the number of electrons in the channel (region immediately under the gate) and hence increases the conductivity of the channel. The operation of a p-type transistor is analogous to the nMOS transistor, with the exception that the majority carriers are holes and the voltages are negative with respect to the substrate. The switching behavior of an MOS device is characterized by threshold voltage, V<sub>t</sub>. This is defined as the voltage at which an MOS device begins to conduct. For gate voltage less than a threshold value, the channel is cut-off, thus causing a very low drain- to-source current. Those devices that are normally cut-off (i.e., non-conducting) with zero gate bias are further classed as enhancement mode devices, whereas those devices that conduct with zero gate bias are called depletion mode devices.

#### MOS Transistor

So far, we have treated MOS transistors as ideal switches.

An *ON* transistor passes a finite amount of current Depends on terminal voltages Need to derive current-voltage (I-V) characteristics.

Transistor gate, source and drain all have capacitance

$$I = C(\Delta V / \Delta t)$$

$$\Delta t = (C/I) \cdot \Delta V$$

We will also look at what a degraded level really means.

Positive/negative voltage applied to the gate (with respect to substrate) enhances the number of electrons/holes in the channel and increases conductivity between source and drain.

$V_t$  defines the voltage at which a MOS transistor begins to conduct. For voltages less than  $V_t$  (threshold voltage), the channel is cut off.

# MOS Terminal Voltages and Modes of Operation

- Mode of operation depends on the terminal voltages. V<sub>g</sub>, V<sub>s</sub>, V<sub>d</sub>

- $\blacksquare$   $V_{gs} = V_g V_s$

- $\blacksquare$   $V_{gd} = V_g V_d$

- $\blacksquare$   $V_{ds} = V_d V_s = V_{gs} V_{gd}$

- O Source and Drain are symmetric diffusion terminals

- By convention, source is terminal at lower voltage

- Hence  $V_{ds} > 0$

- O NMOS body is grounded. First assume that source is 0 too.

- Three modes of operation

- Cutoff

- Linear

- Saturation

# MOS I-V Characteristics (Saturation, linear, cutoff)

# MOS I-V characteristics (saturation)

If  $V_{gd} < V_t$  channel pinches off near the drain

When

$$V_{ds} > V_{dsat} = V_{gs} - V_t$$

Now drain voltage no longer increases current

$$I_{ds} = \beta \left( (V_{gs} - V_t) - \frac{V_{dsat}}{2} \right) V_{dsat} = \frac{\beta}{2} (V_{gs} - V_t)^2$$

# Shockley 1st order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{Cutoff} \\ \beta \Big( (V_{gs} - V_t) - \frac{V_{ds}}{2} \Big) V_{ds} & V_{ds} < V_{dsat} & \text{Linear} \\ \frac{\beta}{2} (V_{gs} - V_t)^2 & V_{ds} > V_{dsat} & \text{Saturation} \end{cases}$$

# MOS I-V Characteristics (Saturation, linear, cutoff)

# MOS I-V characteristics (saturation)

If  $V_{gd} < V_t$  channel pinches off near the drain

When

$$V_{ds} > V_{dsat} = V_{gs} - V_t$$

Now drain voltage no longer increases current

$$I_{ds} = \beta \left( (V_{gs} - V_t) - \frac{V_{dsat}}{2} \right) V_{dsat} = \frac{\beta}{2} (V_{gs} - V_t)^2$$

# Shockley Ist order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{Cutoff} \\ \beta \Big( (V_{gs} - V_t) - \frac{V_{ds}}{2} \Big) V_{ds} & V_{ds} < V_{dsat} & \text{Linear} \end{cases}$$

$$\frac{\beta}{2} (V_{gs} - V_t)^2 & V_{ds} > V_{dsat} & \text{Saturation} \end{cases}$$

# Threshold Voltage

From equations, threshold voltage may be varied by changing:

- The doping concentration (N<sub>A</sub>).

- The oxide capacitance (C<sub>ox</sub>).

- Surface state charge (Q<sub>fc</sub>).

As you can see, it is often necessary to adjust V<sub>t</sub>. Two methods are common:

- Change Q<sub>fc</sub> by introducing a small doped region at the oxide/substrate interface via ion implantation.

- Change Cox by using a different insulating material for the gate.

A layer of Si<sub>3</sub>N<sub>4</sub> (silicon nitride) with a relative permittivity of 7.5 is combined with a layer of silicon dioxide (relative permittivity of 3.9).

This results into a relative permittivity of 6.

For the same thickness dielectric layer, Cox is larger using the combined material, which lowers V<sub>t</sub>.

## **CV Characteristics:**

The measured MOS capacitance (called gate capacitance) varies with the applied gate voltage

- A very powerful diagnostic tool for identifying any deviations from the ideal in both oxide and semiconductor

- Routinely monitored during MMOS device fabrication

Measurement of C-V characteristics

- Apply any dc bias, and superimpose a small (15 mV) ac signal

- Generally measured at 1 MHz (high frequency) or at variable frequencies between 1KHz to 1 MHz

- The dc bias  $V_G$  is slowly varied to get **quasi-continuous** C-V characteristics

# Non-Ideal I-V effects

The I-V characteristics designed so far neglect many effects that are important in modern deep-submicron processes.

Some of these effects include:

- Velocity Saturation and Mobility Degradation

- Channel length modulation

- Subthreshold conduction

- Tunneling

- Junction leakage

- Body Effect (discussed previously)

- Temperature and Geometry dependence

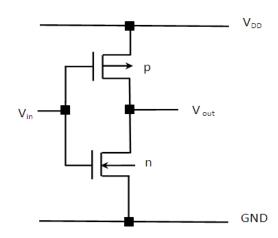

## **DC Characteristics of CMOS inverter**

The general arrangement and characteristics are illustrated in Fig. 2.3. The current/voltage relationships for the MOS transistor may be written as,

$$\begin{split} I_{ds} = K \quad \underline{W} \qquad (V_{ds} - V_t) V_{ds} - \underline{V_{ds}}^2 \\ L \qquad \qquad 2 \end{split} \label{eq:ds_eq}$$

Figure 2.3 CMOS inverter

In the resistive region, or

$$\begin{split} I_{ds} = K \; \underline{W} \; \; & (\underline{V_{gs} - V_t})^2 \\ L \; & 2 \end{split} \label{eq:Ids}$$

In the saturation region. In both cases the factor K is a technology- dependent parameter such that

$$K = \underline{\epsilon_{ins} \; \epsilon_o \; \mu}$$

$$D$$

The factor W/L is contributed by the geometry and it is common practice to write

$$\beta = K \ \underline{W}$$

$$L$$

Such that,

$$I_{ds} = \beta \; (\underline{V_{gs} - V_t})^2 \label{eq:Ids}$$

2

In saturation, and where  $\beta$  may be applied to both nMOS and pMOS transistors as follows,

$$\beta_n = \begin{array}{cc} \epsilon_{\underline{ins}} \; \epsilon_o \; \mu_n & & \underline{W}_n \\ \\ D & & L_n \end{array}$$

$$\beta_p = \begin{array}{ccc} \epsilon_{\underline{ins}} \, \epsilon_o \, \mu_p & W_p \\ \\ D & L_r \end{array}$$

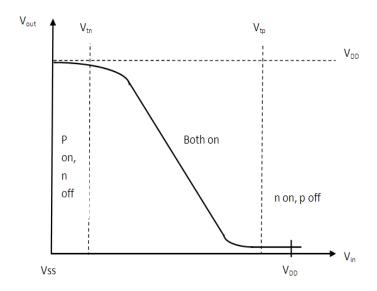

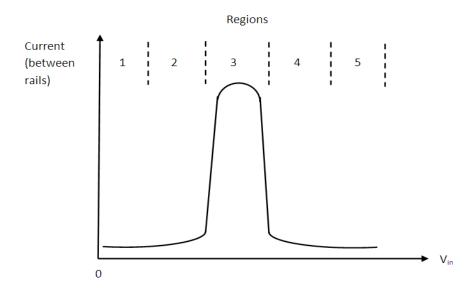

Where  $W_n$  and  $L_n$ ,  $W_p$  and  $L_p$  are the n- and p- transistor dimensions respectively. The CMOS inverter has five regions of operation is shown in Fig. 2.4 and in Fig. 2.5.

Figure 2.4 Transfer characteristics

Considering the static condition first, in region 1 for which  $V_{\rm in}$  = logic 0, the p-transistor fully turned on while the n-transistor is fully turned off. Thus no current flows through the inverter and the output is directly connected to  $V_{\rm DD}$  through the p-transistor.

In region 5  $V_{in}$  = logic 1, the n-transistor is fully on while the p-transistor is fully off. Again, no current flows and a good logic 0 appears at the output.

In region 2 the input voltage has increased to a level which just exceeds the threshold voltage of the n-transistor. The n-transistor conducts and has a large voltage between source and drain. The p-transistor also conducting but with only a small voltage across it, it operates in the unsaturated resistive region.

Figure 2.5 CMOS inverter current versus V<sub>in</sub>

In region 4 is similar to region 2 but with the roles of the p- and n- transistors reversed. The current magnitudes in region 2 and 4 are small and most of the energy consumed in switching from one state to the other is due to the large current which flows in region 3.

In region 3 is the region in which the inverter exhibits gain and in which both transistors are in saturation.

The currents in each device must be the same since the transistors are in series. So we may write

I

$$_{dsp}$$

= - I $_{dsn}$

Where

$$I_{dsp} = \frac{\beta_n \left(V_{in} - V_{DD} - V_{tp}\right)^2}{2}$$

And

$$I_{dsn} = \underline{\beta_n} (V_{in} - V_{tn})^2$$

$V_{in}$  in terms of the  $\beta$  ratio and the other circuit voltages and currents

$$V_{in} = V_{DD} + V_{tp} + V_{tn} \left(\beta_{n} + \beta_{p}\right)^{1/2} \\ \frac{1 + \left(\beta_{n} + \beta_{p}\right)^{1/2}}{1 + \left(\beta_{n} + \beta_{p}\right)^{1/2}}$$

Since both transistors are in saturation, they act as current sources so that the equivalent circuit in this region is two current sources so that the equivalent circuit in this region is two current sources in series between  $V_{DD}$  and  $V_{SS}$  with the output voltage coming from their common point. The region is inherently unstable in consequence and the change over from one logic level to the other is rapid.

If

$$\beta_n = \beta_p$$

and if  $V_{in} = -V_{tp}$ , then

$$V_{in} = 0.5 \ V_{DD}$$

Since only at this point will the two  $\beta$  factors be equal. But for  $\beta_n = \beta_p$  the device geometries must be such that

$$\mu_p W_p/L_p = \mu_n W_n/L_n$$

The mobilities are inherently unequal and thus it is necessary for the width to length ratio of the pdevice to be three times that of the n-device, namely

$$W_p/L_p = 2.5 \ W_n/L_n$$

The mobility  $\mu$  is affected by the transverse electric field in the channel and is thus independent on  $V_{gs}$ . It has been shown empirically that the actual mobility is

$$\mu = \mu_z (1 - Ø (V_{gs} - V_t)^{-1})$$

Ø is a constant approximately equal to 0.05  $V_t$  includes anybody effect, and  $\mu z$  is the mobility with zero transverse field.

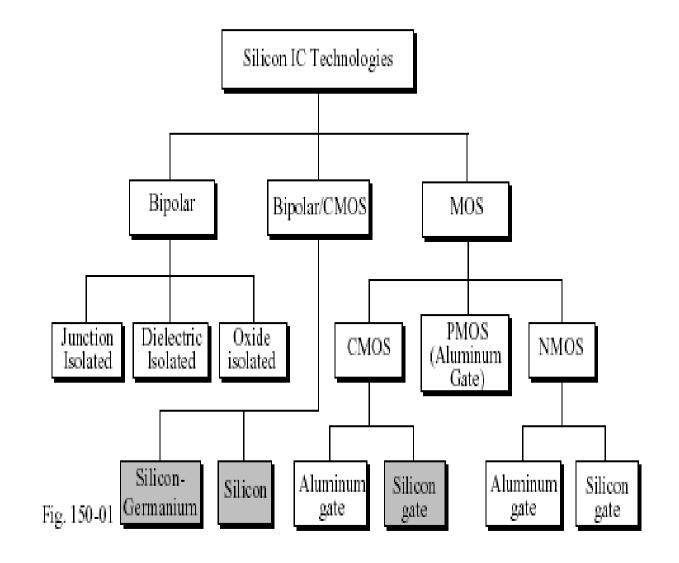

# **CMOS Technologies**

# Classification of Silicon Technology

# **VLSI DESIGN RULES**

(From Physical Design of CMOS Integrated Circuits Using L-EDIT, John P. Uyemura)

# $\lambda = 1 \mu m$

# MINIMUM WIDTH AND SPACING RULES

| LAYER   | TYPE OF RULE                     | VALUE    |

|---------|----------------------------------|----------|

| POLY    | Minimum Width<br>Minimum Spacing | 2λ<br>2λ |

| ACTIVE  | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| NSELECT | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| PSELECT | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| METAL1  | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

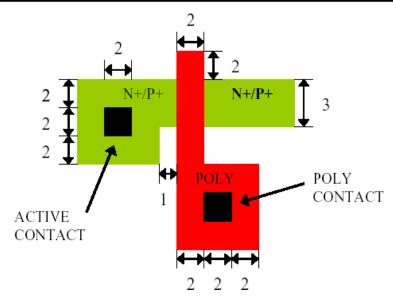

# MOSFET LAYOUT RULES

| RULE           | MEANING                                    | VALUE         |

|----------------|--------------------------------------------|---------------|

| POLY Overlap   | Minimum extension over ACTIVE              | 2λ            |

| POLY-ACTIVE    | Minimum Spacing                            | 1λ            |

| MOSFET Width   | Minimum N+/P+ MOSFET W                     | 3λ            |

| ACTIVE CONTACT | Exact Size<br>Minimum Space to ACTIVE Edge | 2λ x 2λ<br>2λ |

| POLY CONTACT   | Exact Size<br>Minimum Space to POLY Edge   | 2λ x 2λ<br>2λ |

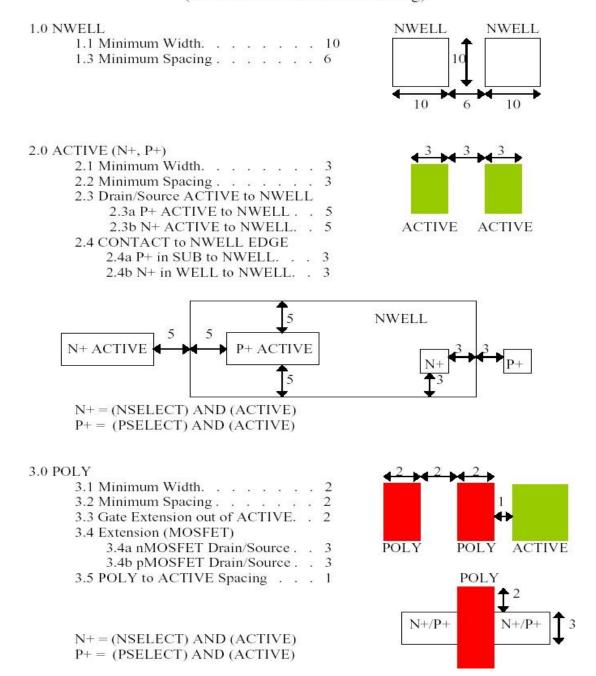

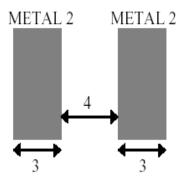

# SCNA DESIGN RULE SET

(Scalable CMOS N-well Analog)

METAL 1

| 4.0 NSELECT and PSELECT  4.2 ACTIVE - SELECT Spacing  4.2a ACTIVE in SELECT 2  4.2b ACTIVE in SELECT to  ACTIVE in next SELECT 2  4.4 Minimum Dimensions  4.4a NSELECT Minimum Width 2  4.4b PSELECT Minimum Width 2  4.4c NSELECT Minimum Space 2  4.4d PSELECT Minimum Space 2  4.5 PSELECT overlap of NSELECT . 0 | ACTIVE  2  1 2                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5.0 POLY CONTACT 5.1 Exact Size 2 x 2 5.2 Field Poly Overlap of POLY CONTACT 2 5.3 Spacing 2                                                                                                                                                                                                                         | POLY CONTACT  POLY  ACTIVE  2  2  2  2 |

| 6.0 ACTIVE CONTACT 6.1 Minimum Width                                                                                                                                                                                                                                                                                 | ACTIVE 2 1 2 2                         |

| 7.0 METAL 1 7.1 Minimum Width                                                                                                                                                                                                                                                                                        | METAL 1 METAL 1                        |

| POLY \$1                                                                                                                                                                                                                                                                                                             | N+/P+                                  |

METAL 1

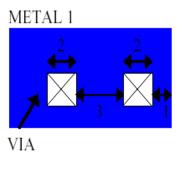

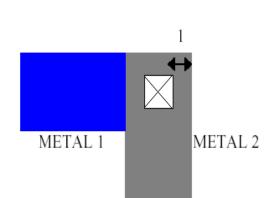

| 3.0 VIA                       |   |

|-------------------------------|---|

| 8.1 Exact Size 2 x            | 2 |

| 8.2 VIA to VIA Spacing        | 3 |

| 8.3 METAL 1 Overlap of VIA    | 1 |

| 8.4 VIA Spacing               |   |

| 8.4a VIA to POLY              | 2 |

| 8.4b VIA (on POLY) to POLY    | 2 |

| 8.4c VIA to ACTIVE            | 2 |

| 8.4d VIA (on ACTIVE) to POLY. | 2 |

|                               |   |

|                               |   |

| 0.0 METAL 2                   |   |

| 9.1 Minimum Width             | 3 |

| 9.2 Minimum Spacing           | 4 |

| 9.3 Overlap of VIA            | 4 |

|                               |   |

#### **CMOS TECHNOLOGIES**

CMOS provides an inherently low power static circuit technology that has the capability of providing a lower-delay product than comparable design-rule nMOS or pMOS technologies. The four dominant CMOS technologies are:

- P-well process

- > n-well process

- > twin-tub process

- > Silicon on chip process

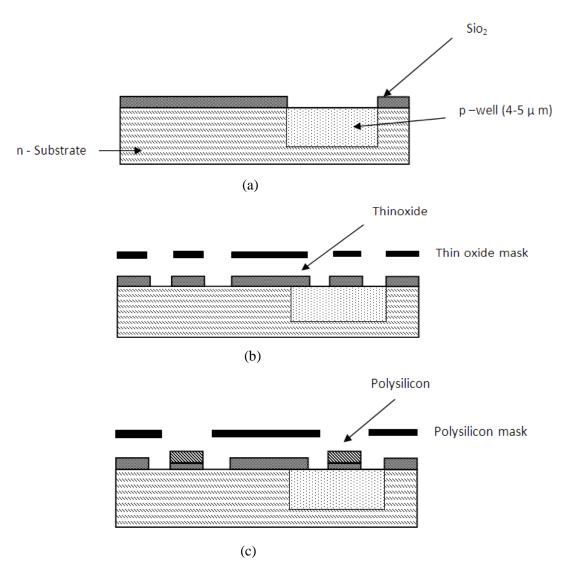

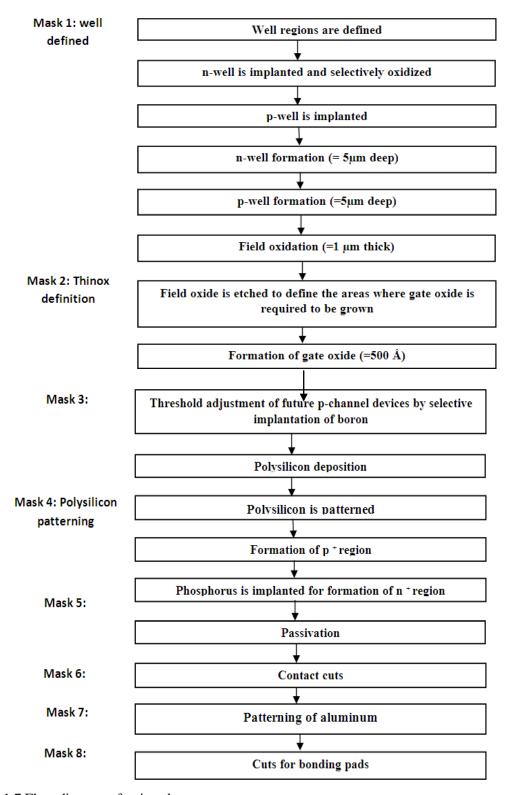

# The p-well process

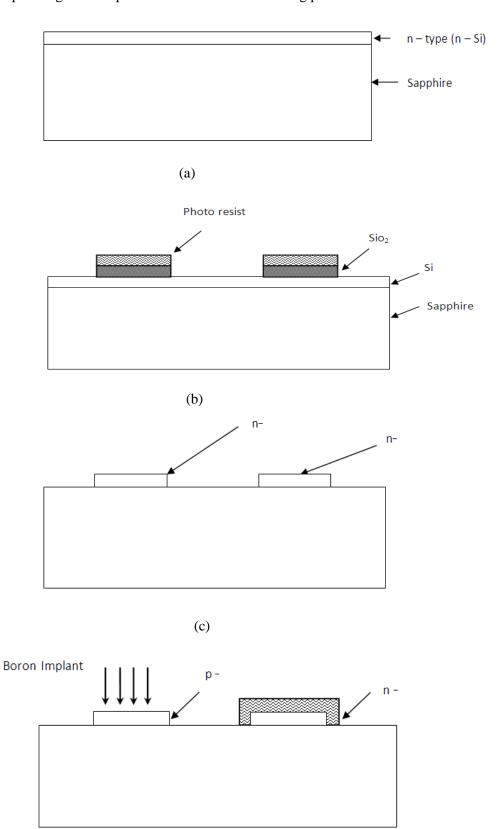

A common approach to p-well CMOS fabrication is to start with moderately doped n-type substrate (wafer), create the p-type well for the n-channel devices, and build the p-channel transistor in the native n-substrate. The processing steps are,

- 1. The first mask defines the p-well (p-tub) n-channel transistors (Fig. 1.5a) will be fabricated in this well. Field oxide (FOX) is etched away to allow a deep diffusion.

- 2. The next mask is called the "thin oxide" or "thinox" mask (Fig. 1.5b), as it defines where areas of thin oxide are needed to implement transistor gates and allow implantation to form por n- type diffusions for transistor source/drain regions. The field oxide areas are etched to the silicon surface and then the thin oxide areas is grown on these areas. O ther terms for this mask include active area, island, and mesa.

- 3. Polysilicon gate definition is then completed. This involves covering the surface with polysilicon (Fig 1.5c) and then etching the required pattern (in this case an inverted "U"). "Poly" gate regions lead to "self-aligned" source-drain regions.

- 4. A p-plus (p<sup>+</sup>) mask is then used to indicate those thin-oxide areas (and polysilicon) that are to be implanted p<sup>+</sup>. Hence a thin-oxide area exposed by the p-plus mask (Fig. 1.5d) will become a p<sup>+</sup> diffusion area. If the p-plus area is in the n-substrate, then a p-channel transistor or p-type wire may be constructed. If the p-plus area is in the p-well, then an ohmic contact to the p-well may be constructed.

- 5. The next step usually uses the complement of the p-plus mask, although an extra mask is normally not needed. The "absence" of a p-plus region over a thin-oxide area indicates that the area will be an n<sup>+</sup> diffusion or n-thinox. n-thinox in the p-well defines possible n-

transistors and wires. An n<sup>+</sup> diffusion (Fig. 1.5e) in the n-substrate allows an ohmic contact to be made. Following this step, the surface of the chip is covered with a layer of Sio2.

- 6. Contacts cuts are then defined. This involves etching any Sio<sub>2</sub> down to the contacted surface, these allow metal (Fig. 1.5f) to contact diffusion regions or polysilicon regions.

- 7. Metallization (Fig. 1.5g) is then applied to the surface and selectively etched.

- 8. As a final step, the wafer is passivated and openings to the bond pads are etched to allow for wire bonding. Passivation protects the silicon surface against the ingress of contaminants.

Figure 1.5 Typical p-well CMOS process steps with corresponding masks required

Basically the structure consists of an n-type substrate in which p-devices may be formed by suitable masking and diffusion and, in order to accommodate n-type devices, a deep p-well is diffused into the n-type substrate. This diffusion must be carried out with special care since the p-well doping concentration and depth will affect the threshold voltages as well as the breakdown voltages of the n-transistors. To achieve low threshold voltage (0.6 to 1.0 V), deep well diffusion or high well resistivity is needed. However, deep wells require larger spacing between the n- and p-type transistors and wires because of lateral diffusion resulting in larger chip areas.

High resistivity can accentuate latch-up problems. In order to achieve narrow threshold voltage tolerances in a typical p-well process, the well concentration is made about one order of magnitude higher than the substrate doping density, thereby causing the body effect for n-channel devices to be higher than for p-channel transistors. In addition, due to this higher concentration, n-transistors suffer from excessive source/drain to p-well capacitance will tends to be slower in performance. The well must be grounded in such a way as to minimize any voltage drop due to injected current in substrate that is collected by the p-well.

The p-well act as substrate for then-devices within the parent n-substrate, and, provided polarity restrictions are observed, the two areas are electrically isolated such that there are in affect two substrate, two substrate connections ( $V_{DD}$  and  $V_{SS}$ ) are required.

## The n-well process:

The p-well processes have been one of the most commonly available forms of CMOS. However, an advantage of the n-well process is that it can be fabricated on the same process line as conventional n MOS. n –well CMOS circuits are also superior to p-well because of the lower substrate bias effects on transistor threshold voltage and inherently lower parasitic capacitances associated with source and drain regions.

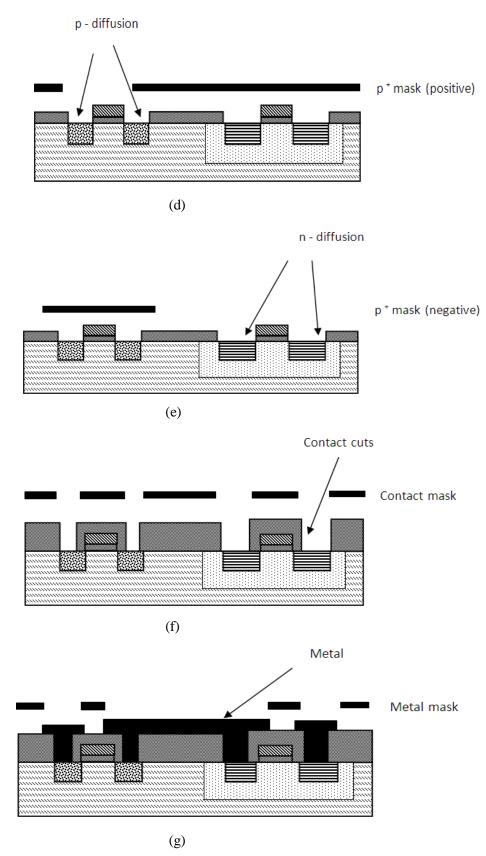

Typically n-well fabrication steps are similar to a p-well process, except that an n-well is used which is illustrated in Fig. 1.6. The first masking step defines the n-well regions. This followed by a low phosphorus implant driven in by a high temperature diffusion step to form the n-wells. The well depth is optimized to ensure against p-substrate to  $p^+$  diffusion breakdown without compromising the n-well to  $n^+$  mask separation. The next steps are to define the devices and diffusion paths, grow field oxide, deposit and pattern the polysilicon, carry out the diffusions, make contact cuts and metallization. An n-well mask is used to define n-well regions, as opposed to a p-well mask in a p-well process. An n-plus  $(n^+)$  mask may be used to define the n-channel transistors and  $V_{DD}$  contacts. Alternatively, we could use a p-plus mask to define the p-channel transistors, as the masks usually are the complement of each other.

Figure 1.6 Main steps in a typical n-well process

Due to differences in mobility of charge carriers the n-well process creates non-optimum p-channel characteristics, such as high junction capacitance and high body effect. The n-well technology has a distinct advantage of providing optimum device characteristics. Thus n-channel devices may be used to form logic elements to provide speed and density, while p-transistors could primarily serve as pull-up devices.

#### The twin-tub process:

Twin-tub CMOS technology provides the basis for separate optimization of the p-type and n-type transistors, thus making it possible for threshold voltage, body effect, and the gain associated with n-and p-devices to be independently optimized. Generally the starting material is either an n<sup>+</sup> or p<sup>+</sup> substrate with a lightly doped epitaxial or epi layer, which is used for protection against latch-up. The aim of epitaxy is to grow high purity silicon layers of controlled thickness with accurately determined dopant concentrations distributed homogeneously throughout the layer. The electrical properties for this layer are determined by the dopant and its concentration in the silicon.

The process sequence, which is similar to the p-well process apart from the tub formation where both p-well and n-well are utilized as in Fig. 1.7, entails the following steps:

#### > Tub formation

- > Thin oxide etching

- Source and drain implantations

- > Contact cut definition

- > Metallization.

Figure 1.7 Flow diagram of twin-tub process

Since this process provides separately optimized wells, better performance n-transistors (lower capacitance, less body effect) may be constructed when compared with a conventional p-well process. Similarly the p-transistors may be optimized. The use of threshold adjust steps is included in this process.

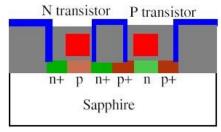

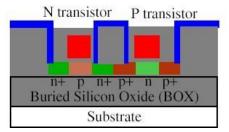

# Silicon on insulator process:

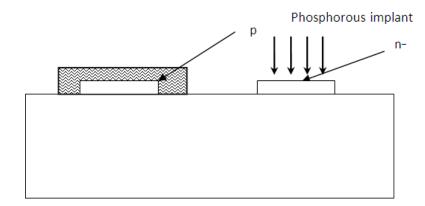

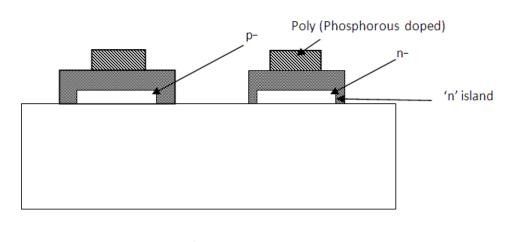

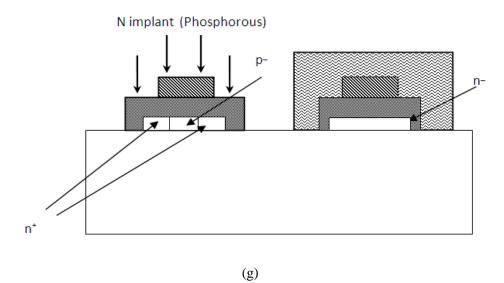

Silicon on insulator (SOI) CMOS processes has several potential advantages such as higher density, no latch-up problems, and lower parasitic capacitances. In the SOI process a thin layer of single crystal silicon film is epitaxial grown on an insulator such as sapphire or magnesium aluminate spinel. The steps involves are:

- 1) A thin film (7-8  $\mu$ m) of very lightly doped n-type Si is grown over an insulator (Fig. 1.8a). Sapphire is a commonly used insulator.

- 2) An anisotropic etch is used to etch away the Si (Fig. 1.8b) except where a diffusion area will be needed.

- 3) The p-islands are formed next by masking the n-islands with a photoresist. A p-type dopant (boron) is then implanted. It is masked by the photoresist and at the unmasked islands. The p-islands (Fig. 1.8c) will become the n-channel devices.

- 4) The p-islands are then covered with a photoresist and an n-type dopant, phosphorus, is implanted to form the n-islands (Fig. 1.8d). The n-islands will become the p-channel devices.

- 5) A thin gate oxide (500-600Å) is grown over all of the Si structures (Fig. 1.8e). This is normally done by thermal oxidation.

- 6) A polysilicon film is deposited over the oxide.

- 7) The polysilicon is then patterned by photomasking and is etched. This defines the polysilicon layer in the structure as in Fig. 1.8f.

- 8) The next step is to form the n-doped source and drain of the n-channel devices in the p-islands. The n-island is covered with a photoresist and an n-type dopant (phosphorus) is implanted (Fig. 1.8g).

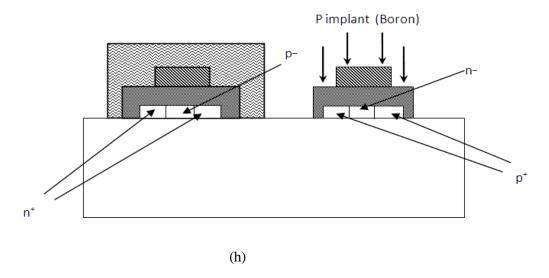

- 9) The p-channel devices are formed next by masking the p-islands and implanting a p-type dopant. The polysilicon over the gate of the n-islands will block the dopant from the gate, thus forming the p-channel devices is shown in Fig. 1.8h.

10) A layer of phosphorus glass is deposited over the entire structure. The glass is etched at contact cut locations. The metallization layer is formed. A final passivation layer of a phosphorus glass is deposited and etched over bonding pad locations.

(d)

(e)

(f)

Figure 1.8 SOI fabrication steps

The advantages of SOI technology are:

- Due to the absence of wells, denser structures than bulk silicon can be obtained.

- ➤ Low capacitances provide the basis of very fast circuits.

- ➤ No field-inversion problems exist.

- No latch-up due to isolation of n- and p- transistors by insulating substrate.

- As there is no conducting substrate, there are no body effect problems

- > Enhanced radiation tolerance.

But the drawback is due to absence of substrate diodes, the inputs are difficult to protect. As device gains are lower, I/O structures have to be larger. Single crystal sapphires are more expensive than silicon and processing techniques tend to be less developed than bulk silicon techniques.

#### **BICMOS TECHNOLOGY FABRICATION**

The MOS technology lies in the limited load driving capabilities of MOS transistors. This is due to the limited current sourcing and current sinking abilities associated with both p- and n- transistors. Bipolar transistors provide higher gain and have generally better noise and high frequency characteristics than MOS transistors and have effective way of speeding up VLSI circuits. When considering CMOS technology, there is difficulty in extending the fabrication processes to include bipolar as well as MOS transistors. Indeed, a problem of p-well and n-well CMOS processing is that parasitic bipolar transistors are formed as part of the outcome of fabrication.

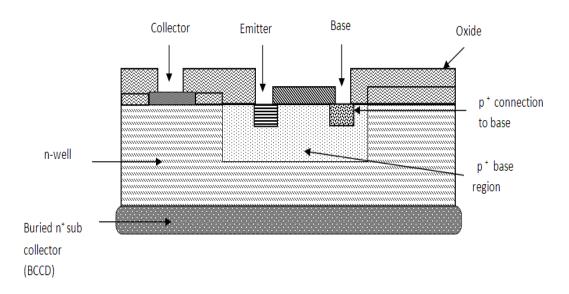

The production of npn bipolar transistors with good performance characteristics can be achieved by extending the standard n-well CMOS processing to include further masks to add two additional layers such as the  $n^+$  subcollector and  $p^+$  base layers. The npn transistors is formed in an n-well and the additional  $p^+$  base region is located in the well to form the p-base region of the transistor. The second additional layer, the buried  $n^+$  subcollector (BCCD), is added to reduce the n-well (collector) resistance and thus improve the quality of the bipolar transistor. The arrangement of BiCMOS npn transistor is shown in Fig. 1.9.

Figure 1.9 Arrangement of BiCMOS npn transistor

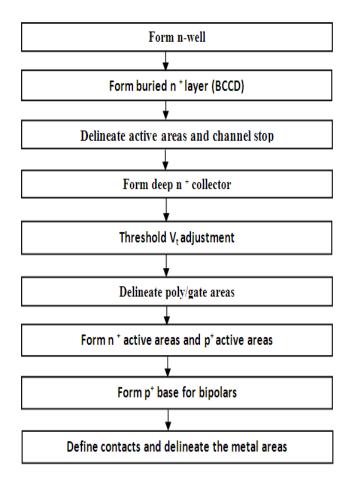

There are several advantages if the properties of CMOS and bipolar technologies could be combined. This is achieved to a significant extent in the BiCMOS technology. A further advantage which arises from BiCMOS technology is that analog amplifier design is facilitated and improved. High impedance CMOS transistors may be used for the input circuitry while the remaining stages and output drivers are realized using bipolar transistors. Since extra design and processing steps are involved as in Fig. 1.10, there is an increase in cost and some loss of packing density.

Figure 1.10 n-well BiCMOS fabrication steps

#### CMOS Process Enhancements

# **Transistors**

Multiple threshold voltages and oxide thicknesses

Processes offer multiple threshold voltages

Low threshold devices: faster, higher leakage. High threshold devices: opposite Thin oxides: provide high ON currents but cannot handle high voltages (e.g. I/Os)

Thicker oxides provided for I/O devices

# ■ Silicon on Insulator

As the name suggests transistors are fabricated on an insulator (SiO<sub>2</sub> or sapphire) Insulating substrate eliminates capacitance between the source/drain and body, higher speed devices and low leakage currents.

# High-k gate dielectrics

Transistors need high gate capacitance to attract charge to the channel

Thin gates and therefore high gate leakages

Thicker gates that leak less can be made with high-k materials

e.g. hafnium oxide (k=20), zirconium oxide (k=23), silicon nitride (k=6.5-7.5)

Applied using ALD, MOCVD (metallo-organic CVD) or sputtering.

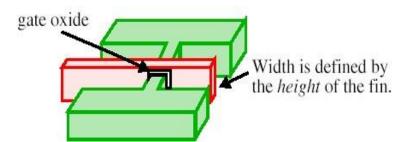

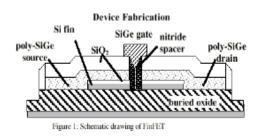

# Low leakage transistors

Scaling transistors causes exponential increase in subthreshold leakages

Can be improved using gate structure where gates is placed on more than one side

of the channel

These devices are generically called *finfets*

# Higher mobility

Achieved by using SiGe (silicon germanium) for bipolar transistors in the same conventional CMOS process

Silicon Germanium can also be used to improve speed by creating strained silicon

## Plastic transistors

MOS transistors fabricated with organic chemicals

Used only for very specific applications as devices are very inexpensive to manufacture

# High-voltage transistors

High voltage MOSFETs can be integrated onto conventional CMOS processes for switching and high-power applications.

Specialized process steps required to achieve very high breakdown voltages.

# Interconnect

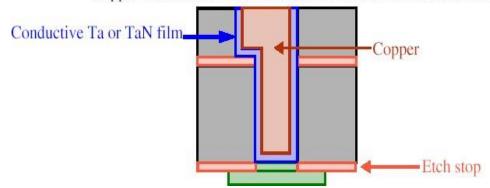

# Copper Damascene process

Using copper (higher conductivity) as interconnect instead of aluminum.

Several challenges due to copper atom diffusion, etching issues and copper oxide formation.

Special barrier layers used to prevent copper from entering the silicon surface.

New metallization process called *Damascene process* invented to form barrier.

Subtractive aluminum based metallization step involved adding aluminum everywhere and then etching it away leaving behind wires.

Copper metallization is additive, trenches are made and then filled with copper.

#### Low-k Dielectrics

Low-k dielectrics between wires are attractive as they decrease wire capacitance. Reduces wire delay and power consumption.

130nm process uses fluorosilicate glass (FSG, flourine added to silicon dioxide). Other materials have been developed, active research area.

## Circuit Elements

Increasing use of CMOS for mixed signal and RF designs, requires special circuit elements with good characteristics

# Capacitors

In conventional CMOS, capacitors can be created using the gate and source/drain, a diffusion area (to ground or  $V_{DD}$ ) or a parallel metal plate capacitor.

Enhancements include addition of a second polysilicon layer.

Other enhanced types include metal-insulator-metal (MiM) capacitor and fringe (fractal) capacitor.

## Resistors

In conventional CMOS, resistors can be built from any layer, where the final resistance depends on the resistivity (resistance per unit area) of the layer.

Large resistance in small areas built using poly or diffusion.

However, poly is usually doped so undoped poly allowed in enhanced processes.

Another enhancement that requires additional processing steps is to allow nichrome that produces high quality resistors.

#### Inductors

Most common monolithic inductor is the spiral inductor, which is a spiral of upper-level metal. Used mainly for RF designs.

Several enhancements techniques used to increase Q (self-resonant frequency).

## Other elements

Other enhancements allow transmission lines, non-volatile memory, bipolar transistors, fuses and antifuses and micro electro mechanical systems (MEMS).

#### **UNIT II CIRCUIT CHARACTERIZATION AND SIMULATION**

#### **Delay estimation:**

Estimation of the delay of a Boolean function from its functional description is an important step towards design exploration at the register transfer level (RTL). This paper addresses the problem of estimating the delay of certain optimal multi-level implementations of combinational circuits, given only their functional description. The proposed delay model uses a new complexity measure called the delay measure to estimate the delay. It has an advantage that it can be used to predict both, the minimum delay (associated with an optimum delay implementation) and the maximum delay (associated with an optimum area implementation) of a Boolean function without actually resorting to logic synthesis. The model is empirical and results demonstrating its feasibility and utility are presented.

From input to rising output crossing VDD/2

tpdf: falling propagation delay

From input to falling output crossing VDD/2

tpd: average propagation delay

tpd = (tpdr + tpdf)/2

tr: rise time

From output crossing 20% to 80% VDD

tf: fall time

From output crossing 80% to 20% VDD

tcd: average contamination delay

tcd = (tcdr + tcdf)/2

tcdr: rising contamination delay: Min from input to rising output crossing VDD/2

tcdf: falling contamination delay: Min from input to falling output crossinVDD/2

Solving differential equations by hand is hard. SPICE like simulators used for accurate analysis. But simulations are expensive. We need to be able to estimate delay although not as accurately as simulator.

Use RC delay models to estimate delay  $C = total \ capacitance \ on \ the \ output \ node$   $Use \ Effective \ resistance \ R$   $Therefore \ tpd = RC$

Transistors are characterized by finding their effective R.

# **Transistor sizing:**

- Not all gates need to have the same delay.

- Not all inputs to a gate need to have the same delay.

- Adjust transistor sizes to achieve desired delay.

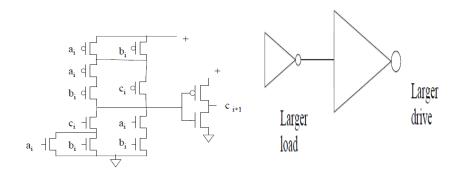

Example: Adder carry chain

Inter-stage effects in transistor sizing

□ Increasing a gate's drive also increases the load to the previous stage

## Logical effort

Logical effort is a gate delay model that takes transistor sizes into account. Allows us to optimize transistor sizes over combinational networks. Isn't as accurate for circuits with reconvergent fanout.

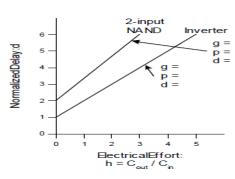

# Logical effort gate delay model

- □ Express delays in process-independent unit

- □ Gate delay is measured in units of minimum-size

$$d=rac{d_{abs}}{ au}$$

$\overset{ au=\ 3RC}{pprox}$   $pprox$  12 ps in 180 nm process inverter delay  $au$ . 40 ps in 0.6  $\mu$ m process

☐ Gate delay formula:

$$d = f + p$$

.

☐ Effort delay f is related to gate's load. Parasitic delay p depends on gate's structure. Represents delay of gate driving no load Set by internal parasitic capacitance

## Effort delay

- $\Box$  Effort delay has two components: f = gh.

- ☐ Electrical effort h is determined by gate's load: h = Cout/Cin Sometimes called fanout

- $\Box$  Logical effort g is determined by gate's structure. Measures relative ability of gate to deliver current  $g \equiv 1$  for inverter

#### **Delay plots:**

$$d = f + p$$

$$= gh + p$$

#### **Computing Logical Effort**

□ Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Measure from delay vs. fanout plots Or estimate by counting transistor widths

# Sizing the transistors

$$D = \sum d_i = D_F + P$$

- Delay is smallest when each stage bears same effort

- Optimal buffer chains are exponentially tapered:

$$\hat{f} = g_i h_i = F^{\frac{1}{N}}$$

- Thus minimum delay of N stage path is  $D = NF^{\frac{1}{N}} + P$

- Determine W/L of each gate on path by working backward from the last gate:  $\hat{f} = gh = g\frac{C_{out}}{C_{c}}$

$$\Rightarrow C_{\mathit{in}_i} = \frac{g_i C_{\mathit{out}_i}}{\hat{f}}$$

#### **Power Estimation:**

The past the major concerns of the VLSI designer were area performance cost and reliability power considerations were mostly of only secondary importance. In recent years however this has begun to change and increasingly power is being given comparable weight to area and speed. Several factors have contributed to this trend Perhaps the primary driving factor has been the remarkable success and growth of the class of personal computing devices portable desktops audio and videobased multimedia products\_ and wireless communications systems \_personal digital assistants and personal communicators\_ which demand high\_speed computation and complex functionality with In the past\_ the major concerns of the VLSI designer were area\_ performance cost and reliability\_ power considerations were mostly of only secondary importance\_ In recent years\_ however\_ this has begun to change and\_ increasingly\_ power is being given comparable weight to area and speed\_ Several factors have contributed to this trend Perhaps the primary driving factor has been the remarkable success and growth of the class of personal computing devices portable desktops audio and video\_based multimedia products and wireless communications systems \_personal digital assistants and personal communicators which demand high\_speed computation and complex functionality with low power consumption. There also exists a strong pressure for producers of high end products to reduce their power consumption.

#### **Software\_Level Power Estimation**

The first task in the estimation of power consumption of a digital system is to identify the typical application programs that will be executed on the system. A non\_trivial application program consumes millions of machine cycles\_ making it nearly impossible to perform power estimation using the complete program at\_ say\_ the RT\_level\_ Most of the reported results are based on power macro\_modeling\_ an estimation approach which is extensively used for behavioral and RTL level estimation see Sections and In the power cost of a CPU module is characterized by estimating the average capacitance that would switch when the given CPU module is activated\_In the switching activities on \_address\_ instruction\_ and data\_ buses are used to estimate the power consumption of the microprocessor, based on actual current measurements of some processors\_ Tiwari et al\_ present the following instruction\_level power model

$$Energy_p = \sum_{i} (BC_i N_i) + \sum_{i,j} (SC_{i,j} N_{i,j}) + \sum_{k} OC_k$$

where Energyp is the total energy dissipation of the program which is divided into three parts The first part is the summation of the base energy cost of each instruction, BCi is the base energy cost and Ni is the number of times instruction i is executed. The second part accounts for the circuit state SCi\_j is the energy cost when instruction i is followed by j during the program execution\_Finally\_ the third part accounts for energy contribution OCk of other instruction effects such as stalls and cache misses during the program execution\_ In Hsieh et al\_ present a new approach\_ called profile driven program

synthesis\_ to perform RT\_level power estimation for high performance CPUs\_ Instead of using a macro\_modeling equation to model the energy dissipation of a microprocessor\_ the authors use a synthesized program to exercise the microprocessor in such a way that the resulting instruction trace behaves \_in terms of performance and power dissipation\_ much the same as the original trace\_ The new instruction trace is however much shorter than the original one\_ and can hence be simulated on a RT\_level description of the target microprocessor to provide the power dissipation results quickly\_ Specifically\_ this approach consists of the following steps\_

- Perform architectural simulation of the target microprocessor under the instruction trace of typical application programs\_

- Extract a characteristic pro\_le\_ including parameters such as the instruction mix\_ Instruction data cache miss rates\_ branch prediction miss rate\_ pipeline stalls\_ etc\_ for the microprocessor.

- Use mixed integer linear programming and heuristic rules to gradually transform a generic program template into a fully functional program\_

- Perform RT\_level simulation of the target microprocessor under the instruction trace of the new synthesized program \_

Notice that the performance of the architectural simulator in gate vectors second is roughly to orders of magnitude higher than that of a RT\_level simulator. This approach has been applied to the Intel Pentium processor \_which is a super\_ scalar pipelined CPU with \_KB \_way set\_associative data\_ instruction and data caches\_ branch prediction and dual instruction pipeline\_ demonstrating \_ to \_ orders of magnitude reduction in the RT\_level simulation time with negligible estimation error.

## **Behavioral\_Level Power Estimation**

Conversely from some of the RT\_level methods that will be discussed in Section estimation techniques at the behavioral\_level cannot rely on information about the gatelevel structure of the design components\_ and hence\_ must resort to abstract notions of physical capacitance and switching activity to predict power dissipation in the design\_

#### **Information\_Theoretic Models**

Information theoretic approaches for high\_level power estimation depend on information theoretic measures of activity .for example\_ entropy\_ to obtain quick power estimates Entropy characterizes the randomness or uncertainty of a sequence of applied vectors and thus is intuitively related to switching activity\_ that is\_ if the signal switching is high\_ it is likely that the bit sequence is random\_ resulting in high entropy\_ Suppose the sequence contains t distinct vectors and let pi denote the occurrence probability of any vector v in the sequence\_ Obviously\_

The entropy of the sequence is given

$$h = -\sum_{i=1}^{t} p_i \log p_i$$

where  $\log x$  denotes the base logarithm of x\_ The entropy achieves its maximum value of  $\log t$  when pi  $\log$  pi For an n\_bit vector(t,n)his makes the computation of the exact entropy very expensive. Assuming that the individual bits in the vector are independent then we can write

$$h = -\sum_{i=1}^{n} (q_i \log q_i + (1 - q_i) \log(1 - q_i))$$

where qi denotes the signal probability of bit i in the vector sequence. Note that this equation is only an upperbound on the exact entropy, since the bits may be dependent. This upperbound expression is\_ however\_ the one that is used for power estimation purposes. Furthermore in it has been shown that\_ under the temporal independence assumption\_ the average switching activity of a bit is upper\_bounded by one half of its entropy

The power dissipation in the circuit can be approximated as

$$Power = 0.5V^2 f C_{tot} E_{avg}$$

Where Ctot is the total capacitance of the logic module including gate and interconnect capacitances\_ and Eavg is the average activity of each line in the circuit which is inturn approximated by one half of its average entropy havg. The average line entropy is computed by abstracting information obtained from a gate\_level implementation. In it is assumed that the word\_level entropy per logic level reduces quadratically from circuit inputs to circuit outputs\_ whereas in it is assumed that the bit\_level entropy from one logic level to next decreases in an exponential manner. Based on these assumptions two different computational models are obtained

In Marculescu et al\_ derive a closed\_form expression for the average line entropy for the case of a linear gate distribution(i.e.,)when the number of nodes scales linearly between the number of circuit inputs n and circuit outputs m. The expression for havg is given by

$$h_{avg} = \frac{2nh_{in}}{(n+m)\ln\frac{h_{in}}{h_{out}}} \left(1 - \frac{m}{n} \frac{h_{out}}{h_{in}} - \frac{(1 - \frac{m}{n})(1 - \frac{h_{out}}{h_{in}})}{\ln\frac{h_{in}}{h_{out}}}\right)$$

where hin and hout denote the average bit\_level entropies of circuit inputs and outputs\_respectively\_ hin is extracted from the given input sequence\_ whereas hout is calculated from a quick functional simulation of the circuit under the given input sequence or by empirical entropy propagation techniques for pre\_characterized library modules. In Nemani and Najm propose the following expression for havg

$$h_{avg} = \frac{2}{3(n+m)} (H_{in} + H_{out})$$

where Hin and Hout denote the average sectional \_word\_level\_ entropies of circuit inputs and outputs\_ respectively\_ The sectional entropy measures Hin and Hout may be obtained by monitoring the input and output signal values during a high\_level simulation of the circuit\_ In practice\_ however\_

they are approximated as the summation of individual bit\_level entropies\_ hin and hout. If the circuit structure is given\_ the total module capacitance is calculated by traversing the circuit netlist and summing up the gate loadings\_ Wire capacitances are estimated using statistical wire load models\_ Otherwise\_ Ctot is estimated by quick mapping for example\_ mapping to\_\_input universal gates\_ or by information theoretic models that relate the gate complexity of a design to the di\_erence of its input and output entropies. One such model proposed by Cheng and Agrawal in for example estimates

$$C_{tot} = \frac{m}{n} 2^n h_{out}$$

This estimate tends to be too pessimistic when n is large hence in Ferrandi et al\_ present a new total capacitance estimate based on the number N of nodes i.e.,to multiplexors in the Ordered Binary Decision Diagrams OBDD representation of the logic circuit as follows

$$C_{tot} = \alpha \frac{m}{n} N h_{out} + \beta$$

The coefficients of the model are obtained empirically by doing linear regression analysis on the total capacitance values for a large number of synthesized circuits. Entropic models for the controller circuitry are proposed by Tyagi in where three entropic lower bounds on the average Hamming distance \_bit changes\_ with state set S and with T states\_ are provided. The tightest lower bound derived in this paper for a sparse \_nite state machine FSM i.e., tT log T where t is the total number of transitions with nonzero steady\_state probability\_ is the following

$$\sum_{s_i, s_j \in S} p_{i,j} H(s_i, s_j) \ge h(p_{i,j}) - 1.52 \log T - 2.16 + 0.5 \log(\log T)$$

where pi,j is the steady state transition probability from si to sj H(si,sj) is the Hamming distance between the two states\_ and h(pi,j) is the entropy of the probability distribution pi,j. Notice that the lower bound is valid regardless of the state encoding used. In using a Markov chain model for the behavior of the states of the FSM\_ the authors derive theoretical lower and upper bounds for the average Hamming distance on the state lines which are valid irrespective of the state encoding used in the final implementation. Experimental results obtained for the mcnc benchmark suite show that these bounds are tighter than the bounds reported.

#### **Design Margin:**

As semiconductor technology scales to the nanometer regime, the variation of process parameters is a critical problem in VLSI design. Thus the need for variation-aware timing analysis for the performance yield is increasing. However, the traditional worst-case corner-based approach gives pessimistic results, and makes meeting given designs specifications difficult. As an alternative to this approach, statistical analysis is proposed as a new and promising variation-aware analysis technique. However, statistical design flow cannot be applied easily to existing design flow, and not enough tools for statistical design exist. To overcome these problems, new design methodology based on traditional static timing analysis (STA) using a relaxed corner proposed

nowadays. This paper investigates the effects of corner relaxation on overall circuit performance metrics (yield, power, area) at the gate/transistor levels. Experimental results indicate that if we design the circuit using relaxed corner, though the circuit yield is somewhat reduced, we can get some advantages in area and power aspects.

# **Reliability:**

Yield and reliability are two of the cornerstones of a successful IC manufacturing technology along with product performance and cost. Many factors contribute to the achievement of high yield and reliability, and many of these also interact with product performance and cost. A fundamental understanding of failure mechanisms and yield limitations enables the up-front achievement of these technology goals through circuit and layout design, device design, materials choices, process optimization, and thermo-mechanical considerations. Failure isolation and analysis, defect analysis, low yield analysis, and materials analysis are critical methodologies for the improvement of yield and reliability. Coordination of people in many disciplines is needed in order to achieve high yield and reliability. Each needs to understand the impact of their choices and methods on the final product. Unfortunately, very little formal university training exists in these critical areas of IC reliability, yield, and failure analysis.

### **Reliability Fundamentals and Scaling Principles**

- The Reliability Bathtub Curve, Its Origin and Implications

- Key Reliability Functions and Their Use in Reliability Analysis

- Defect Screening Techniques and Their Effectiveness

- Accelerated Testing and Estimation of Useful Operating Life

- Reliability Data Collection and Analysis in Integrated Circuits

- Past Technology Scaling Trends

- Forward Looking Projections with a Focus on Examining and Understanding of the Impact on VLSI Reliability

- Power Density Trends: Operating temperature, activation energies for dominant vlsi failure mechanisms, and reliability impact

- Reliability Strategies In Fabless Environments

### **Reliability of the Interconnect System**

- Physics and Statistics of Failure Mechanisms Associated with Interconnect Systems

- Electro-migration of Al and Cu Interconnects

- Mechanical Stress Driven Metal Voiding and Cracking

- Low k Materials as Interlayer Dielectrics and Their Impact on Electro-migration

- Thermo-mechanical Integrity of the Interconnect System

- Key Technology Parameters: Materials choices, structural and geometric effects

- Extreme Scaling Impact on Wear-out Time

- Technology Solutions: Alloys, metal barriers, and engineering of interfaces

- Improved Electro-migration Performance under Non-DC Currents and Short Lines

- Interconnect Reliability Strategies in Fabless Environments

# Transistor Reliability: Dielectric Breakdown, Hot Carriers and Parametric Stability

- Physics, Statistics, and Scaling Impact on Failure Mechanisms

- Reliability Performance of Thin Conventional Oxides: Defects, wear-out failures

- Hot Carrier Performance and Parametric Stability of P- and N-channel Devices under DC and AC

- High k Gate Dielectrics and Novel Transistor Configurations

- Key Failure Mechanisms for Bipolar Transistors

- Transistor Reliability Strategies in Fabless Environments

# **CMOS Latch-up and ESD**

- Physics, Scaling Impact, and Technology Dependence of CMOS Latch-up and Electrostatic Damage (ESD)

- Technology and Design Based Solutions, Device Performance, and Manufacturability Constraints

- Latch-up and ESD Assessment in Fabless Environments

# **Soft Errors, and Other Failure Mechanisms**

- Physics, Scaling Impact, and Technology Dependence of Alpha Particle and Cosmic Ray Induced Soft Errors

- Technology Solutions, Performance, and Manufacturability

# **Scaling:**

In scaling there are really two issues

• Devices

- Can we build smaller devices

- What will their performance be

- Wires

- Try to avoid the wet noodle effect

- There is concern about our ability to scale both of these Components

# Limitations

Limitations to device scaling has been around since working in 3m nMOS, 22 years ago (actually bipolar)

- Worries were

- Short channel effect

- Punchthrough

- drain control of current rather than gate

- Hot electrons

- Parasitic resistances

- Now worries are a little different

- Oxide tunnel currents

- Punchthrough

- Parameter control

- Parasitic resistances

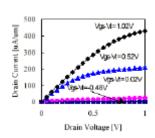

### **Transistor scaling:**

People are building very short channel devices

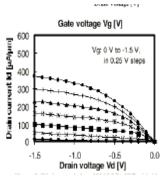

- Shown are I-V curves for 15nm L pMOS

- And a short channel nMOS

- The structure is strange

- FinFET

- But you can make them work

# Wire scaling:

More uncertainty than transistor scaling

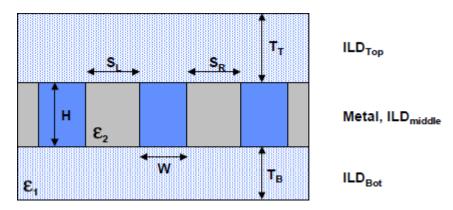

- Many options with complex trade-offs

- For each metal layer

- Need to set H, TT, TB, e1, e2, conductivity of the metal

# **SPICE Tutorial:**

# 1.Introduction

Given below is a brief introduction to simulation using HSPICE and AWAVES/Cosmoscope in the UTD network. HSPICE is a device level circuit simulator from Synopsys. HSPICE takes a SPICE file as input and produces output describing the requested simulation of the circuit. The simulation output can be viewed with AWAVES (or) Cosmoscope from Synopsys. A short example is provided to illustrate the basic procedures involved in running HSPICE.

# 2. Setting up your account to access HSPICE

This section shows how to setup your environment for running HSPICE.

For users who have a working CAD setup, you may just want to check that the LM\_LICENSE\_FILE has the following values in the list of all the other licenses, /home/cad/flexlm/ti-license:/home/cad/flexlm/hspice.flx. If not, follow the procedures below: Instructions for both bash and tcsh/csh users is provided here:

#### bash users:

Add the following line to the .bash\_profile

$LM\_LICENSE\_FILE=\$LM\_LICENSE\_FILE:/home/cad/flexlm/hspice.flx\ ;\ export\ LM\_LICENSE\_FILE$

tcsh/csh users:

Add the following line to your .tcshrc

setenv LM\_LICENSE\_FILE \${LM\_LICENSE\_FILE}:/home/cad/flexlm/hspice.flx

To test if the above procedure has setup your environment successfully, invoke a new shell (this will ensure that the new environment variables are in place). Also you will need a HSPICE input file to test this (You can copy paste the HSPICE example given below to test this). The input Spice file is typically named with extension \*.sp.

% hspice <your\_input\_file>.sp

The following message indicates **trouble** with invocation:

If the error is "hspice: command not found" make sure that the HSPICE

directory ''/home/cad/synopsys/hspice/U-2003.09-SP1/sun58/" is included

in the \$PATH variable.

Cannot execute /home/cad/synopsys/hspice/U-2003.09-SP1/sun58/hspice

or

lic: Using FLEXIm license file:

lic: /home/cad/flexlm/hspice.flx

lic: Unable to checkout hsptest

The above error may indicate that the license server maybe down, or the machine is not able to run HSPICE.

On the other hand if the procedure was successful, you will simply see a message indicating successful completion of simulation or errors in simulation, both of which indicate HSPICE has run your file.

# 3. Setting up the HSPICE input file

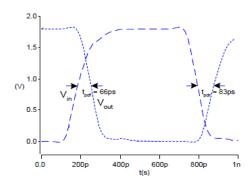

Consider a self loaded min geometry inverter circuit. The objective of the HSPICE input file below is to measure the  $t_{pLH}$  and  $t_{pHL}$  both graphically and otherwise. The following HSPICE file is stored in "inv.sp". The HSPICE input file is commented adequately about the different options used in it.

It will be beneficial to keep in mind the following differences between SPICE3 and HSPICE.

| Property              | SPICE3                                                                                                                             | HSPICE                                                                                                                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transistor dimensions | Default Scale is 1u.Hence depending on model, with or without "u".Eg. l=20                                                         | If units are not specified and no SCALE statement is present, the scale defaults to <i>meters</i> . Hence for HSPICE always specify units. Eg. 1=20u                                                                                                                                                          |

| Input bit<br>Pattern  | PBIT or PWL                                                                                                                        | Only PWL format is supported. Howevere to convert a PBIT(Bit stream format) to a PWL form, you can use the script and help at the following page: <a href="http://www.utdallas.edu/~poras/courses/ee6325/lab/hspice/pbit2pwl.html">http://www.utdallas.edu/~poras/courses/ee6325/lab/hspice/pbit2pwl.html</a> |

| Output format         | Print and Punch files produced only if requested as .punch/.print. SIMG reads the .pun file                                        | SIMG does not read HSPICE output, only AWAVES or Cosmoscope can read HSPICE output. Also a graphical output produced only if .option post=1 is provided. The .print command is of no consequence to graphical output.                                                                                         |

| Line continuation     | In order to specifying a continuing line '&' character is used at the end of the first line. Eg: Vin in gnd PWL& Ons pvdd 1ns pvdd |                                                                                                                                                                                                                                                                                                               |

# **HSPICE Example File:**

\* Parametric definitions

| * Self loaded min geometry inverter, sample HSPICE file         |

|-----------------------------------------------------------------|

| * Include the model files                                       |

| * Include the hspice model files for 0.18u technology.          |

| include /home/cad/vlsi/models/hspice/cmos0.18um.model           |

| **************************************                          |

| * The subcircuit for the inverter                               |

| subckt invert in out vdd gnd                                    |

| param length=0.2u                                               |

| m01 out in vdd vdd pfet w='4*length' l='length'                 |

| m02 out in gnd gnd nfet w='1.5*length' l='length'               |

|                                                                 |

| ends                                                            |

| **************************************                          |

| * The main inverter                                             |

| X1 in out vdd gnd invert                                        |

| * Four loads for the inverter                                   |

| X2 out out1 vdd gnd invert                                      |

| X3 out out2 vdd gnd invert                                      |

| X4 out out3 vdd gnd invert                                      |

| X5 out out4 vdd gnd invert                                      |

| FWL pattern for the input, represents a bit stream 1100101      |

| * Slew=1ns, bit time=5ns                                        |

| Vin in gnd PWL 0ns pvdd 1ns pvdd 5ns pvdd 6ns pvdd 7ns 0 10ns 0 |

| + 15ns 0 16ns pvdd 21ns pvdd 22ns 0 25ns 0 26ns pvdd            |

|                                                                 |

```

.param pvdd=2.0v

```

```

* Power supplies

vvdd vdd 0 pvdd

vgnd gnd 0 0

```

\* Control statements

```

.option post=1

```

.TR 0.05ns 30ns

.print TR V(in out)

- \* Measure statements help in calculating TPLH, TPHL etc, without

- \* opening the waveform viewer

```

.measure tran tplh trig v(in) val='0.5*pvdd' fall=1 targ v(out) val='0.5*pvdd' rise=1 .measure tran tphl trig v(in) val='0.5*pvdd' rise=1 targ v(out) val='0.5*pvdd' fall=1

```

.END

### 4. Running HSPICE simulations

The following commands can be used to simulate the above HSPICE file stored in **inv.sp** and store all the simulation results with file prefix as "**inv**"

# % hspice inv.sp -o inv

This results in the creation of the following output files:

inv.ic -> Operating point node voltages (initial conditions)

inv.lis -> Output listing

inv.mt0 -> Transient analysis measurement results

inv.pa0 -> Subcircuit cross-listing

inv.st0 -> Output status

inv.tr0 -> Transient analysis results

# 5. Analyzing the outputs

In the above example, the output data can be analyzed both graphically as well as in text form.

# **Text outputs:**

To view the results of the .measure computation, execute:

### % cat inv.mt0

\$DATA1 SOURCE='HSPICE' VERSION='2003.09-SP1'

.TITLE''

tplh tphl temper alter#

3.416e-10 1.002e-09 25.0000 1.0000

As can be seen above, the values of propogation delay have been obtained even before the waveform analysis software has been opened.

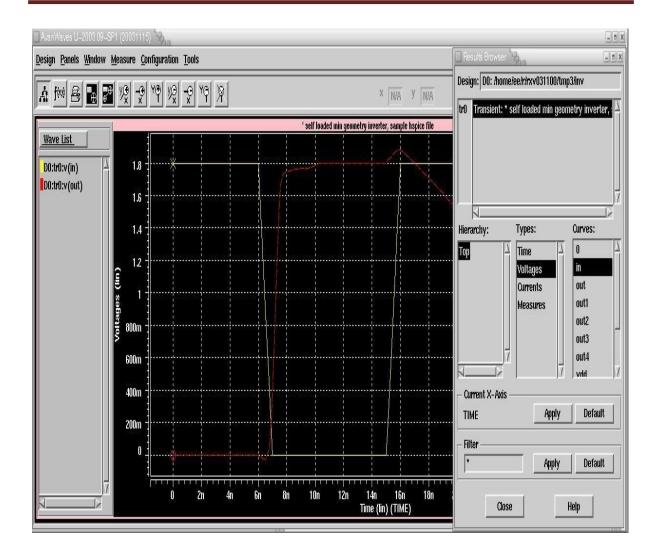

### **Graphical outputs:**

### I. Synopsys Awaves:

To invoke AWAVES run the following command:

% awaves

If you get the error "awaves: command not found" make sure that the AWAVES directory "/home/cad/synopsys/hspice/U-2003.09-SP1/sun58/" is included in the \$PATH variable.

Once invoked, open the design using the pull down menu options: Design>Open and select inv.sp and then highlight the tr0 (Transient response) item in the select box. You

will also see the hierarchy of the netlist and the types of analysis and the individual signals in separate

lists in the window. Select Hierarchy -> Top, Types -> Voltages and select the voltages you want to

observe For eg. in and out by double clicking on the names. You will see the screen below for the

stimulus provided in inv.sp.

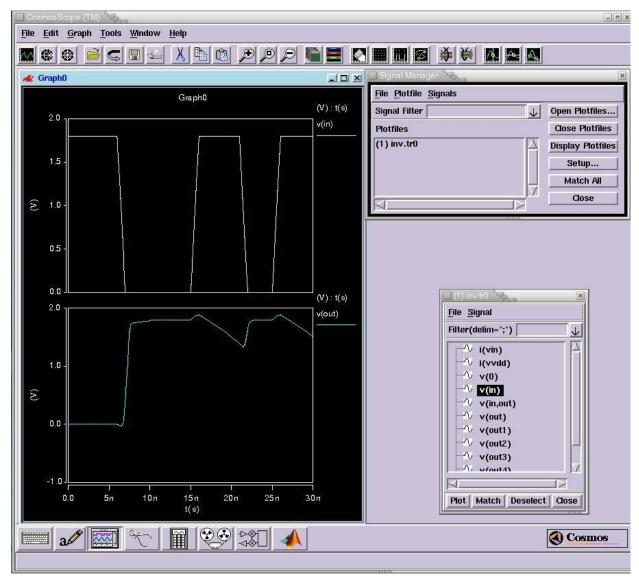

# II. Synopsys Cosmoscope:

To invoke Cosmoscope run the following command:

# %cscope

If you get the error "awaves: command not found" make sure that the AWAVES directory "/home/cad/synopsys/cosmo/ai\_bin/" is included in the \$PATH variable.

Once invoked, open the design using the pull down menu options: File -> Open -> Plotfiles and select file inv.tr0 in the working directory. A Signal Manager window and signal window opens. Select the necessary signals to be plotted by double-clicking them. For example v(in) and v(out) by double clicking on the signal names in the signal window. You will see the below for the stimulus provide screen

d in inv.sp.

#### **Device models:**

The motivation for this investigation stems from three main concerns:

- 1. The usual parameterization of device models for device and circuit simulation causes problems due to the interdependence of the parameters. It is not physically realistic to change any one parameter without determining the change in the process technology that would produce such a change in the parameter. Then all the other parameters which also depend on this change in the technology must be adjusted accordingly. In addition, it is quite difficult to determine the effect of a specific change in a new technology since the available parameters each depend on a number of technology parameters.

- 2. The predictive performance of present models is not good. It has usually been necessary to fabricate devices in any chosen technology, and extract parameters, and then fit the model to this specific technology by use of additional "adjustment" parameters. Of course, this procedure is

reasonable and useful once a technology has been chosen. However, it would be useful if the model could produce fairly accurate results if only the process specifications are used. Without such predictive accuracy it is difficult to make an initial choice of technology.

3. Most models have been developed for digital applications where devices operate above threshold and therefore are not strongly temperature sensitive. This causes problems for modeling analog circuits which use subthreshold operation. In particular, the temperature dependence of subthreshold behavior has not been fully explored. In many models some parameters which are temperature dependent have been assumed to be constant. Device and circuit models are all based on the physical properties of semiconductor materials, the dimensions of the devices, and on theoretical and empirical equations which are intended to model electrical behavior. The distinction between theoretical and empirical equations is often unclear. Most of the equations are substantially empirical. Of all the equations, one of the most fundamental, and problematic, is the equation for ni, the intrinsic carrier concentration of a semiconductor. The definition of ni derives from the thermodynamic equilibrium of electron and hole formation, based on the fact that the energy gap is a Gibbs energy. The equilibrium equation is

$$np = N_c N_v e^{-\frac{E_g}{kT}}$$

$n_i = (np)^{1/2}$

where n is the electron concentration, p is the hole concentration, Nc is the density of effective states in the conduction band, Nv is the density of effective states in the valence band, Eg is the band gap, k is Boltzmann's constant and T is the absolute temperature. The carrier concentration is then given by It would appear to be a simple matter to substitute Si values for Nc, Nv, Eg, and the value of the constant kT to obtain an accurate value of ni. However, the theoretical and experimental knowledge required for accurate values of Nc and Nv is even now incomplete. In the early 1960's, when Si-based circuits were beginning to be designed and fabricated very little was known about Nc and Nv, but estimates were required for practical use. This led to approximations based on work. The key approximation was that chosen by Grove in . This approximation is the still widely used

$$n_i = 1.45 \times 10^{10}$$

at  $T = 300K$

### **Determination of Intrinsic Carrier Concentration (ni)**

The empirical expressions for Eg from Bludau and for Nc and Nv from Sproul and Green provide the values needed for equation (2.1). Our derivation of the equation for ni follows Green. Therefore, the exciton binding energy term, using the value Exb = 14.7meV, is included in the band gap, Eg. In the past, this term has either been neglected, or in some cases a value of 10meV has been

used. Green [9] and Sproul and Green are by far the best references for the history, theory, and experimental measurements leading to reliable values for ni. Thus, the equations are:

$$E_{g0} = 1.1700eV$$

$$E_{g} = E_{g0} + 1.059e^{-5T} - 6.05e^{-7T^{2}} \qquad (0 < T < 190K)$$

$$E_{g} = 1.1785 - 9.025e^{-5T} - 3.05e^{-7T^{2}} \qquad (150 < T <= 300K)$$

$$n_{i} = 1.640 \times 10^{15T^{1.706}} e^{-\frac{E_{g}}{2kT}}.$$

### Circuit and device characterization:

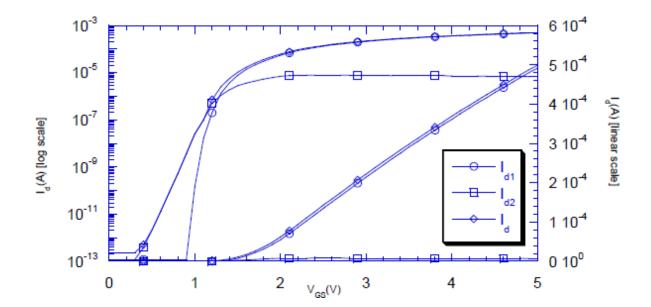

The modeling procedure is introduced in this chapter, taking into consideration the requirements for a *good* MOSFET analog model, discussed in the previous chapter. We note here two main aspects of our modeling approach;

- a. The model must describe *accurately* all the operating regions in order to be integrated in a circuit simulator.

- b. The current, conductance, and transconductance must be continuous in all regions of operation.

Our main goal in this chapter is to determine the drain current for any combination of terminal voltages. The chapter is divided into two main parts. Throughout the first part, it is assumed that the channel is sufficiently *long* and *wide*, so that edge effects are confined to a negligible part of it. While in the second part we incorporate the short and narrow channel effects to the model. We also assume that the substrate is *uniformly* doped. The doping concentration will be assumed to be *p*-type and the modification to non uniform doping will be discussed later in this chapter.

### **Gradual Channel approximation (GCA)**

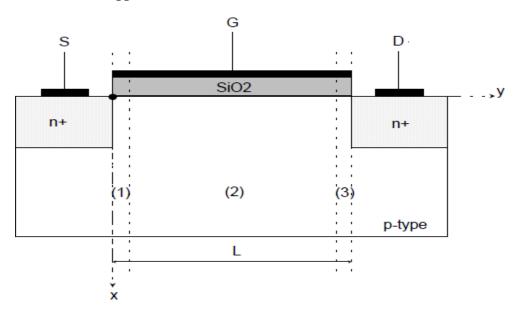

Figure 2.1 The MOSFET structure.

Analytical or semi-analytical modeling of MOSFET characteristics is usually based on the so-called *Gradual Channel Approximation* (GCA). In this approximation, we assume that the gradient of the electric field in the y direction,  $\partial F/\partial y$  is much smaller than the gradient of the electric field in the x direction,  $\partial F/\partial x$ . Which enable us to determine the inversion and depletion

charge densities under the gate in terms of a one-dimensional electrostatic problem for the direction perpendicular to the channel. By applying of the two dimensional Poisson's equation for the semiconductor, refer to Fig. 2.1 region (2),

$$\frac{\partial F_x}{\partial x} + \frac{\partial F_y}{\partial y} = \frac{\rho}{\varepsilon_z}$$

(2.2.1)

if we assume that the GCA is valid equation 2.2.1 may be approximated to the following one dimensional differential equation

$$\frac{\partial F_x}{\partial x} \approx \frac{\rho}{\varepsilon_s}$$

(2.2.2)

we approach the source and drain junctions, the GCA becomes invalid (Fig. 2.1 regions (1) and (3)) because of the increasing longitudinal field due to the pn junctions which make  $\partial F/\partial y$  comparable or even larger than  $\partial F/\partial x$ . However, for the long channel MOSFET's these transition regions can be neglected with respect to the total length of the device. In order to account for the effect of these regions, it is necessary to use two dimensional analysis requiring a numerical solution of 2.2.1.

### Validity of the GCA

The validity of GCA can be checked by making rough estimates of the variation in the longitudinal and vertical field components. We will establish expressions that allow the GCA to be checked under strong inversion.

$$\frac{\partial F_{x}/\partial x}{\partial F_{y}/\partial y} = \left(\frac{\varepsilon_{ox}L}{\varepsilon_{si}}\right)^{2} \frac{q(V_{GS} - V_{T})^{2}}{kT.t_{ox}^{2}.V_{DS}} >> 1$$

(2.2.3)

For a MOSFET at 300K with  $L=1.0\mu m$ , tox = 30 nm, VGS-VT = 0.5, and VDS = 0.5 V, the left hand side of inequality 2.2.3 is  $\sim$  2300, indicating that the GCA is a very good approximation for such a MOSFET. This also implies that the GCA can be valid even in submicron MOSFETs, provided that VGSVT is not too small.

#### 2.3 The long channel current model

The derivation of the dc drain current relationship recognizes that, in general, the current in the channel of a MOSFET can be caused by both drift and diffusion current. In an NMOSFET we may assume the following resonable approximation:

- i- The drain current is mainly carried by electrons.

- ii- The current flows almost in the y direction.

iii- No sources or sinks in the channel.

Note that in weak inversion the surface potential along the channel in long channel MOSFETs is almost constant. Thus  $\partial Fy/\partial y$  is very small, implying that  $\partial Fy/\partial y << \partial Fx/\partial x$ . Thus in long channel MOSFET the GCA is valid both in strong and weak inversion regions . Which enable us to reach to the following general relationship of drain current.

# General Drift-Diffusion current equation in MOSFET:

This is the drift-diffusion drain current of the form

$$I_{D}(y) = \mu_{n} W(-Q_{i}) \frac{d \phi_{c}}{dy} = \mu_{n} W(-Q_{i}(y)) \frac{d \psi_{s}(y)}{dy} + \mu_{n} W \phi_{t} \frac{dQ_{i}(y)}{dy}$$

(2.3.1)

where  $\mu n$  is the electron surface mobility in the channel, W is the channel width, Qi is the inversion charge density per unit area,  $\varphi c$  is the quasi Fermi potential (the difference between Efn at the surface of the semiconductor a d Efp in the bulk of the semiconductor),  $\psi s$  is the surface potential referenced to the bulk potential, and  $\varphi t$  is the thermal voltage (=kT/q). The first term is the *drift current component*, while the second term is the *diffusion current component*. In both components,  $\mu n$  is the electrons' surface mobility being less than the mobility in the bulk due to surface scattering.

### Voltage-Charge equation from the Transverse electric field:

In order to eliminate the electron charge density Qi term in the current charge equation, a second relationship is required that relates the electron charge density to the applied potentials. Using the relationship between voltage and charge appearing across the MOS capacitor we have

$$Cox (VG - \phi ms - \psi s) = -(Qi + QB + Qox + Qit) (2.3.2)$$

where VG is the gate voltage referenced to the bulk potential,  $\phi ms$  is the metal semiconductor work function difference, QB is the depletion (bulk impurity) charge density per unit area, Qox is the sum of the effective net oxide charge per unit area at the Si-SiO2 interface, and Qit is the interface trapped charge density per unit area. Different approximations have been introduced in order to express the different MOS charges (QB, Qox, Qit) in terms of the applied voltages, then

using eq. (2.3.2) to compute the inversion charge density *Qi*. The resulting charge is then used in eq. (2.3.1) to determine the drain current; Four main approaches then follow, after them we shall discuss the proposed approach recently developed in ICL1 and modified by this work.

#### **Interconnect simulation models:**

### The classical long-channel Pao and Sah model

The Pao-Sah model [11,14], published in 1966, was the first advanced long channel MOSFET model to be developed. While it retained the GCA, it didn't invoke the depletion approximation and permitted carrier transport in the channel by both drift and diffusion current. The formulation of the

drain current equation is therfore general, but as a result requires numerical integration in two dimensions, which limits its application in CAD tools.

### Approximations:

- i. Gradual Channel Approximation is used.

- ii . Constant mobility is assumed.

- iii . Uniform substrate doping is considered.

# Advantages:

- i. It is physically based.

- ii . It gives a continuous representation of the device characteristics from weak to strong inversion even to the saturation mode of operation.

### Disadvantages:

i. It requires excessive computational requriments since it requires numerical integration in two dimension, rendering it unsuitable to be used for circuit CAD.

### The charge-sheet based models